EMI降低技術和基于FPGA的可編程振蕩器抖動處理

來源:http://www.sdyoujian.cn 作者:億金電子 2019年06月24

如今FPGA是包含的復雜系統許多功能塊,通常是多個時鐘用來驅動不同的塊.系統設計師有決定如何結合外部振蕩器和用于優化時鐘樹設計的內部資源.這個論文將討論今天可用的選項時鐘速度和抖動要求,重點關注可編程時鐘振蕩器作為時序參考用于基于FPGA的系統.主題包括靈活性由高分辨率頻率選擇產生,EMI降低技術和基于FPGA的抖動清潔工.

1、簡介

復雜的FPGA包含大型功能陣列需要與每個通信的塊或單元其他進行廣泛的復雜操作.除基本邏輯陣列外,還有FPGA包括內部存儲器(RAM),DSP模塊,處理器,鎖相環(PLL)和延遲-用于定時生成的鎖定循環(DLL),標準I/O,高速數字收發器和并行接口(PCI,DDR等).

許多設計使用多個時鐘來驅動不同的塊,每個可能需要不同的晶振頻率.這些時鐘通常使用生成外部振蕩器和內部振蕩器的組合PLL和DLL,取決于時鐘速度和抖動要求.某些功能的時鐘速度是由應用決定,而設計師可以選擇系統其 他部分的頻率.

2、多個時鐘頻率

與I/O接口相關的時鐘需要運行行業標準頻率以確保不同系統之間的互操作性.例子包括100MHz用于PCI Express,75MHz用于PCI或33.333MHz用于PCI.用戶通常可以選擇時鐘的頻率驅動處理器或狀態機引擎.這個彈性-ibility允許設計人員選擇頻率優化速度,功率或資源使用.

在優化速度時,它可能看起來很直轉發使用可能的最高頻率最大化每秒的操作次數.該但是,時鐘周期抖動必須足夠低最小時鐘周期大于設計中的關鍵時序路徑.

FPGA中的內部PLL可用于合成來自較低頻率的較高頻率時鐘外部參考振蕩器.這可能是有效的PLL有高電平時頻率選擇的方法頻率分辨率和低抖動.低噪聲,小數N分頻PLL可以滿足大多數規格由簡單的外部振蕩器驅動.

但是,許多FPGA使用帶環的整數PLL壓控振蕩器(VCO)因為它們易于設計,功耗極低.該這種類型的PLL壓控晶振的問題是權衡在頻率分辨率和抖動之間.

典型的整數PLL包括預分頻器(P),反饋分頻器(M)和后分頻器(N),如圖所示在圖1中.輸出頻率由定義等式1.

而輸出抖動取決于相位噪聲參考時鐘和內部VCO都是內部VCO的貢獻通常占主導地位.PLL的帶寬越高,則越低VCO相位噪聲和整體抖動越低.最大PLL帶寬定義為a預分配比的函數如下:

一個更保守的帶寬值,在指定實際PLL時常用的是由等式3給出:

通常,增加帶寬以改善抖動可取的.一個問題是P的值很大通常需要達到足夠高的頻率分辨率,限制最大PLL帶寬.

3、優化PLL設計

一種允許高頻率的方法分辨率和低抖動是使用可編程的振蕩器作為外部參考.這降低了在提供所需性能的同時對內部PLL提出要求.可編程外部振蕩lators可以使用更高頻率的參考可以降低所需的預分頻率,允許更高PLL帶寬.

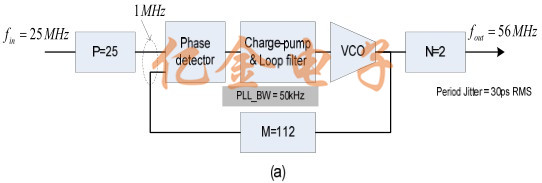

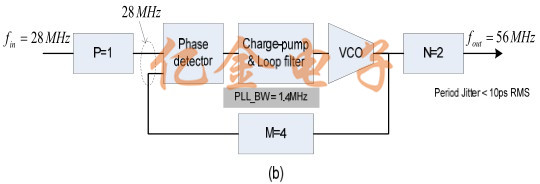

例如,考慮一個需要56的應用程序具有10ps RMS抖動的MHz時鐘晶振.圖2顯示兩種設計,一種使用標準的25MHz參考另一個使用非標準的28MHz參考來自可編程振蕩器.

設計a需要較大的P值,從而產生一個帶寬為50kHz(由公式3計算)并且抖動為30ps,這超出了規范.設計b利用頻率程序-能夠選擇允許的輸入頻率預分頻比為1,產生PLL帶寬為1.4MHz.抖動小于10ps rms,符合規定的要求.

可編程振蕩器可包括石英晶體諧振器或硅MEMS諧振器,但基于MEMS的振蕩器lators具有易于獲得的優點在各種行業標準的塑料包裝和任何所需的輸入頻率.他們提供成本-滿足抖動要求的有效解決方案要求嚴格的FPGA應用 圖2. 兩種PLL設計:(a)標準頻率參考時鐘和(b)靈活的頻率參考時鐘,允許更高的PLL帶寬和更低的抖動

1、簡介

復雜的FPGA包含大型功能陣列需要與每個通信的塊或單元其他進行廣泛的復雜操作.除基本邏輯陣列外,還有FPGA包括內部存儲器(RAM),DSP模塊,處理器,鎖相環(PLL)和延遲-用于定時生成的鎖定循環(DLL),標準I/O,高速數字收發器和并行接口(PCI,DDR等).

許多設計使用多個時鐘來驅動不同的塊,每個可能需要不同的晶振頻率.這些時鐘通常使用生成外部振蕩器和內部振蕩器的組合PLL和DLL,取決于時鐘速度和抖動要求.某些功能的時鐘速度是由應用決定,而設計師可以選擇系統其 他部分的頻率.

2、多個時鐘頻率

與I/O接口相關的時鐘需要運行行業標準頻率以確保不同系統之間的互操作性.例子包括100MHz用于PCI Express,75MHz用于PCI或33.333MHz用于PCI.用戶通常可以選擇時鐘的頻率驅動處理器或狀態機引擎.這個彈性-ibility允許設計人員選擇頻率優化速度,功率或資源使用.

在優化速度時,它可能看起來很直轉發使用可能的最高頻率最大化每秒的操作次數.該但是,時鐘周期抖動必須足夠低最小時鐘周期大于設計中的關鍵時序路徑.

FPGA中的內部PLL可用于合成來自較低頻率的較高頻率時鐘外部參考振蕩器.這可能是有效的PLL有高電平時頻率選擇的方法頻率分辨率和低抖動.低噪聲,小數N分頻PLL可以滿足大多數規格由簡單的外部振蕩器驅動.

但是,許多FPGA使用帶環的整數PLL壓控振蕩器(VCO)因為它們易于設計,功耗極低.該這種類型的PLL壓控晶振的問題是權衡在頻率分辨率和抖動之間.

典型的整數PLL包括預分頻器(P),反饋分頻器(M)和后分頻器(N),如圖所示在圖1中.輸出頻率由定義等式1.

而輸出抖動取決于相位噪聲參考時鐘和內部VCO都是內部VCO的貢獻通常占主導地位.PLL的帶寬越高,則越低VCO相位噪聲和整體抖動越低.最大PLL帶寬定義為a預分配比的函數如下:

一個更保守的帶寬值,在指定實際PLL時常用的是由等式3給出:

通常,增加帶寬以改善抖動可取的.一個問題是P的值很大通常需要達到足夠高的頻率分辨率,限制最大PLL帶寬.

3、優化PLL設計

一種允許高頻率的方法分辨率和低抖動是使用可編程的振蕩器作為外部參考.這降低了在提供所需性能的同時對內部PLL提出要求.可編程外部振蕩lators可以使用更高頻率的參考可以降低所需的預分頻率,允許更高PLL帶寬.

例如,考慮一個需要56的應用程序具有10ps RMS抖動的MHz時鐘晶振.圖2顯示兩種設計,一種使用標準的25MHz參考另一個使用非標準的28MHz參考來自可編程振蕩器.

設計a需要較大的P值,從而產生一個帶寬為50kHz(由公式3計算)并且抖動為30ps,這超出了規范.設計b利用頻率程序-能夠選擇允許的輸入頻率預分頻比為1,產生PLL帶寬為1.4MHz.抖動小于10ps rms,符合規定的要求.

可編程振蕩器可包括石英晶體諧振器或硅MEMS諧振器,但基于MEMS的振蕩器lators具有易于獲得的優點在各種行業標準的塑料包裝和任何所需的輸入頻率.他們提供成本-滿足抖動要求的有效解決方案要求嚴格的FPGA應用 圖2. 兩種PLL設計:(a)標準頻率參考時鐘和(b)靈活的頻率參考時鐘,允許更高的PLL帶寬和更低的抖動

正在載入評論數據...

相關資訊

- [2024-11-09]溫度補償晶體振蕩器 JT21LE,功耗極低...

- [2023-06-26]Rakon推出RakonXpress品牌的現成頻率...

- [2023-06-20]Cardinal晶振公司環境政策,CSM1Z-A0B...

- [2023-06-20]Cardinal晶振ROSH證明,CX532Z-A2B3C5...

- [2023-06-17]為什么選擇ClearClock有源晶振,AK2AD...

- [2021-01-21]低功耗性能且含數字溫度補償的時鐘IC...

- [2020-12-04]TXC晶振車規級頻率組件最新產品應用方...

- [2020-10-19]石英振蕩器系列六——產品未來應用市...

銷售代表

銷售代表