如何巧妙設計削頂正玄波至CMOS的轉換電路?

來源:http://www.sdyoujian.cn 作者:億金電子 2020年06月16

如何巧妙設計削頂正玄波至CMOS的轉換電路?

其實從一定意義上來說,想要設計晶振產品的輸出邏輯由削頂正玄波轉向CMOS的轉換電路是非常簡單的,只是通常情況下很少有人會注意到這樣的問題,哪怕注意到了,這樣的念頭也只是曇花一現.那么削頂正弦波向CMOS轉換的電路到底需要怎樣設計呢? 我們這里討論的削頂正玄波以及CMOS都是指有源晶振的輸出邏輯,說到石英晶體振蕩器的輸出邏輯我們不得不來盤一下它了,因為可能會有很多朋友對此知之甚少,晶振的輸出邏輯種類繁多,下面我們一一介紹

1)TTL:Transistor-Transistor Logic(晶體管-晶體管邏輯電路),傳輸延遲時間快、功耗高,屬于電流控制器件.

2)CMOS:Complementary Metal Oxide Semiconductor(互補金屬氧化物半導體CMOS邏輯電路),傳輸延遲時間慢、功耗低,屬于電壓控制器件.

3)ECL:Emitter-CoupleLogic(發射極耦合邏輯電路),該電路的特點是基本門電路工作在非飽和狀態.ECL電路具有相當高的速度,平均延遲時間可達幾個毫微秒甚至亞毫微秒數量級.ECL電路的邏輯擺幅較小(僅約0.8V,而TTL的邏輯擺幅約為2.0V),當電路從一種狀態過渡到另一種狀態時,對寄生電容的充放電時間將減少,這是ECL電路具有高開關速度的重要原因.但ECL輸出的邏輯擺幅小,對抗干擾能力不利.另外ECL電路具有很高的輸入阻抗和低的輸出阻抗.

4)PECL:PosiTIve Emitter-Couple Logic(正發射極耦合邏輯電路).ECL電路速度快,驅動能力強,噪聲小,很容易達到幾百MHz的應用,但是功耗大,需要負電源.

5)LVDS:Low-Voltage DifferenTIal Signaling(低電壓差分信號),為差分對輸入輸出,內部有一個恒流源3.5~4mA,在差分線上改變方向和電平來表示”1”和”0”.通過外部的100歐匹配電阻(并接在差分線上靠近接收端)轉換為±350mV的差分電平.

6)Clipped Sine Wave:削頂正弦波(Clipped Sine Wave).相比方波的諧波分量少很多,但驅動能力較弱,在負載10K//10PF時Vp-p為0.8Vmin.通常為SMD7050、SMD5032、3225貼片晶振等封裝的表貼溫補晶振使用的輸出波形.

7)SinWave:通常晶振正弦波輸出的負載阻抗為50歐姆.波形的諧波分量很小,一般諧波抑制都優于-30dBc.正弦波輸出晶振通常用于射頻信號處理、頻率源等應用場合.

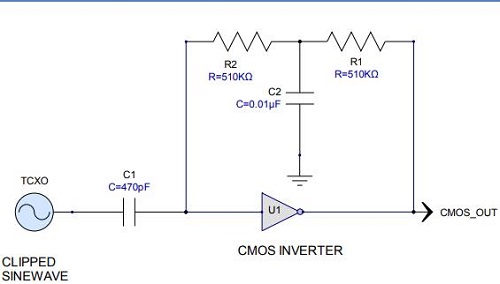

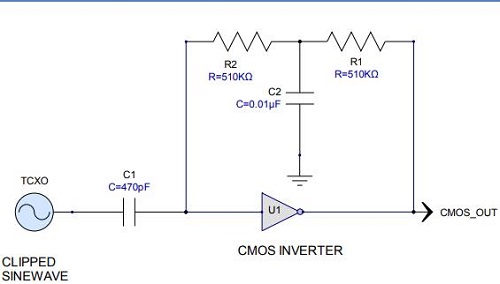

可見削頂正弦波與CMOS屬于不同類別的輸出方式的,具體的轉換電路如下圖所示.

上述電路將削波的正弦波波形轉換為CMOS波形.CMOS反相器選擇必須針對工作頻率進行額定.正確選擇逆變器,該電路可以在高達100MHz的頻率下工作.

上述電路將削波的正弦波波形轉換為CMOS波形.CMOS反相器選擇必須針對工作頻率進行額定.正確選擇逆變器,該電路可以在高達100MHz的頻率下工作.

但是還存在一定的缺陷,特別是對于溫補晶振來說影響會比較大,由于該電路與CMOS反相器的輸出隔離,因此它給TCXO帶來了恒定的負載.由R1,R2和C2組成的反饋網絡可以用一個1Meg歐姆的電阻代替,但是TCXO將被CMOS反相器的輸出跳變拉動.

其實從一定意義上來說,想要設計晶振產品的輸出邏輯由削頂正玄波轉向CMOS的轉換電路是非常簡單的,只是通常情況下很少有人會注意到這樣的問題,哪怕注意到了,這樣的念頭也只是曇花一現.那么削頂正弦波向CMOS轉換的電路到底需要怎樣設計呢? 我們這里討論的削頂正玄波以及CMOS都是指有源晶振的輸出邏輯,說到石英晶體振蕩器的輸出邏輯我們不得不來盤一下它了,因為可能會有很多朋友對此知之甚少,晶振的輸出邏輯種類繁多,下面我們一一介紹

1)TTL:Transistor-Transistor Logic(晶體管-晶體管邏輯電路),傳輸延遲時間快、功耗高,屬于電流控制器件.

2)CMOS:Complementary Metal Oxide Semiconductor(互補金屬氧化物半導體CMOS邏輯電路),傳輸延遲時間慢、功耗低,屬于電壓控制器件.

3)ECL:Emitter-CoupleLogic(發射極耦合邏輯電路),該電路的特點是基本門電路工作在非飽和狀態.ECL電路具有相當高的速度,平均延遲時間可達幾個毫微秒甚至亞毫微秒數量級.ECL電路的邏輯擺幅較小(僅約0.8V,而TTL的邏輯擺幅約為2.0V),當電路從一種狀態過渡到另一種狀態時,對寄生電容的充放電時間將減少,這是ECL電路具有高開關速度的重要原因.但ECL輸出的邏輯擺幅小,對抗干擾能力不利.另外ECL電路具有很高的輸入阻抗和低的輸出阻抗.

4)PECL:PosiTIve Emitter-Couple Logic(正發射極耦合邏輯電路).ECL電路速度快,驅動能力強,噪聲小,很容易達到幾百MHz的應用,但是功耗大,需要負電源.

5)LVDS:Low-Voltage DifferenTIal Signaling(低電壓差分信號),為差分對輸入輸出,內部有一個恒流源3.5~4mA,在差分線上改變方向和電平來表示”1”和”0”.通過外部的100歐匹配電阻(并接在差分線上靠近接收端)轉換為±350mV的差分電平.

6)Clipped Sine Wave:削頂正弦波(Clipped Sine Wave).相比方波的諧波分量少很多,但驅動能力較弱,在負載10K//10PF時Vp-p為0.8Vmin.通常為SMD7050、SMD5032、3225貼片晶振等封裝的表貼溫補晶振使用的輸出波形.

7)SinWave:通常晶振正弦波輸出的負載阻抗為50歐姆.波形的諧波分量很小,一般諧波抑制都優于-30dBc.正弦波輸出晶振通常用于射頻信號處理、頻率源等應用場合.

可見削頂正弦波與CMOS屬于不同類別的輸出方式的,具體的轉換電路如下圖所示.

但是還存在一定的缺陷,特別是對于溫補晶振來說影響會比較大,由于該電路與CMOS反相器的輸出隔離,因此它給TCXO帶來了恒定的負載.由R1,R2和C2組成的反饋網絡可以用一個1Meg歐姆的電阻代替,但是TCXO將被CMOS反相器的輸出跳變拉動.

正在載入評論數據...

相關資訊

- [2024-11-09]溫度補償晶體振蕩器 JT21LE,功耗極低...

- [2023-06-26]Rakon推出RakonXpress品牌的現成頻率...

- [2023-06-20]Cardinal晶振公司環境政策,CSM1Z-A0B...

- [2023-06-20]Cardinal晶振ROSH證明,CX532Z-A2B3C5...

- [2023-06-17]為什么選擇ClearClock有源晶振,AK2AD...

- [2021-01-21]低功耗性能且含數字溫度補償的時鐘IC...

- [2020-12-04]TXC晶振車規級頻率組件最新產品應用方...

- [2020-10-19]石英振蕩器系列六——產品未來應用市...

銷售代表

銷售代表