同時具備差分輸出的雙輸出晶體振蕩器應用分析

來源:http://www.sdyoujian.cn 作者:億金電子 2019年08月01

石英晶體振蕩器我們最簡單的理解就是相比晶體諧振器多了自身的電壓.晶體振蕩器可以細分為SPX0振蕩器,VCXO壓控晶體振蕩器,TCXO溫度補償晶體振蕩器,OCXO恒溫振蕩器等.下面億金電子給大家介紹同時具備差分輸出的雙輸出晶體振蕩器.

對于諸如無線手機中的本地振蕩器(LO),鎖相LO中的頻率參考或微處理器或數據采集系統中的主時鐘源之類的應用,通常需要高質量頻率源(即振蕩器).

對于系統設計人員來說,重要的信號源參數是頻率精度和頻率穩定性.精度與頻率的初始值有關,穩定性與溫度和老化影響的頻率相位噪聲(短期)和漂移(長期)有關.對于晶體振蕩器設計人員來說,關鍵參數是諧振器本身的參數:諧振頻率,電抗和Q因子.除了相位噪聲之外,這些參數幾乎完全是晶體的函數.

低相位噪聲取決于諧振器和有源元件.諧振器應具有高Q值(大多數晶體在10,000至50,000范圍內具有極高的Q值).有源晶振應具有低閃爍噪聲和低噪聲系數,并且其在諧振器上的負載應該是最小的.這些屬性描述了MAX2620 IC中的有源器件:它具有高頻雙極性工藝固有的低閃爍噪聲,低噪聲系數和低寄生rb,其有源器件上的最小負載保持高負載Q值在振蕩器電路中需要.圖1顯示了一個簡單的晶體振蕩器.

選擇晶體諧振器的主要標準是標稱頻率,初始頻率精度和頻率穩定性與溫度和老化的關系.在實踐中,設計人員應注意晶體諧振器的中心頻率,Q值,運動電阻和負載電容.這些參數使設計人員能夠計算振蕩器電路外部電容的值.

在圖1b中晶體諧振器(X1)是Statek的表面貼裝基模器件.需要運動阻力值來計算圖1a中C3和C4的值,但最壞情況(高)值優于典型值.在這種情況下,設備制造商規定最大運動電阻為150Ω.為了啟動振蕩,該值應小于有源器件的輸入負電阻(RIN=-gmXC3XC4)的幅度; 參見圖1a.

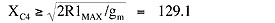

作為一種良好的做法,它應該不到一半.因此,gmXC3XC4>2R1MAX

其中

gm是有源器件跨導.在這種情況下,它等于18毫秒(18毫西門子).

XC3是電容器C3(1/2πfC3)的電抗.

XC4是電容器C4(1/2πfC4)的電抗.

R1MAX(150Ω)是晶體諧振器的最大動態電阻.

重新排列并選擇XC3=XC4,

在10MHz,C3和C4的(假定相等)是值:

C3=C4=1/2πf X C4=123.3pF

選擇行業標準電容值為120pF,石英晶體諧振器兩端的負載電容為C3和C4的串聯:1/(1/C3+1/C4)=60pF.但是,為確保在所需頻率下振蕩,必須通過指定的負載電容(20pF)加載晶體諧振器.這可以通過將C3和C4的值各自降低到40pF來實現,但結果是非常大的過量增益(RIN + R1MAX),這可能對振蕩器的噪聲性能有害.設置20pF凈負載電容的首選方法是引入一個30pF串聯電容(圖1b完成電路中的C5 ).

集電極開路引腳有效-低OUT和OUT(引腳5和8)提供差分輸出或兩個單端輸出.每個引腳可吸收大約2.5mA的靜態電流,每個引腳都需要上拉至VCC.RF扼流圈或電阻可用作上拉電阻,但對于差分輸出,請務必在每條線上使用相同的類型.請注意,大于100Ω的電阻上拉會導致電壓過低.對于50Ω負載,單端輸出電平約為-6dBm(320mVP-P),具有RF扼流圈上拉,約-13dBm(140mVP-P),具有50Ω電阻上拉.

對于諸如無線手機中的本地振蕩器(LO),鎖相LO中的頻率參考或微處理器或數據采集系統中的主時鐘源之類的應用,通常需要高質量頻率源(即振蕩器).

對于系統設計人員來說,重要的信號源參數是頻率精度和頻率穩定性.精度與頻率的初始值有關,穩定性與溫度和老化影響的頻率相位噪聲(短期)和漂移(長期)有關.對于晶體振蕩器設計人員來說,關鍵參數是諧振器本身的參數:諧振頻率,電抗和Q因子.除了相位噪聲之外,這些參數幾乎完全是晶體的函數.

低相位噪聲取決于諧振器和有源元件.諧振器應具有高Q值(大多數晶體在10,000至50,000范圍內具有極高的Q值).有源晶振應具有低閃爍噪聲和低噪聲系數,并且其在諧振器上的負載應該是最小的.這些屬性描述了MAX2620 IC中的有源器件:它具有高頻雙極性工藝固有的低閃爍噪聲,低噪聲系數和低寄生rb,其有源器件上的最小負載保持高負載Q值在振蕩器電路中需要.圖1顯示了一個簡單的晶體振蕩器.

圖1.這個簡單的晶體振蕩器基于單個振蕩器IC.晶體諧振器X1如(b)所示.

MAX2620的其他特性包括有源晶體振蕩器元件,包括緩沖放大器,可最大限度地降低振蕩器頻率的負載,在+2.7V至+5.25V范圍內的電源電壓下工作,電源不敏感的內部偏置,關斷能力以及兩個開路-收集器輸出,可配置為兩個單端輸出或單個差分輸出.選擇晶體諧振器的主要標準是標稱頻率,初始頻率精度和頻率穩定性與溫度和老化的關系.在實踐中,設計人員應注意晶體諧振器的中心頻率,Q值,運動電阻和負載電容.這些參數使設計人員能夠計算振蕩器電路外部電容的值.

在圖1b中晶體諧振器(X1)是Statek的表面貼裝基模器件.需要運動阻力值來計算圖1a中C3和C4的值,但最壞情況(高)值優于典型值.在這種情況下,設備制造商規定最大運動電阻為150Ω.為了啟動振蕩,該值應小于有源器件的輸入負電阻(RIN=-gmXC3XC4)的幅度; 參見圖1a.

作為一種良好的做法,它應該不到一半.因此,gmXC3XC4>2R1MAX

其中

gm是有源器件跨導.在這種情況下,它等于18毫秒(18毫西門子).

XC3是電容器C3(1/2πfC3)的電抗.

XC4是電容器C4(1/2πfC4)的電抗.

R1MAX(150Ω)是晶體諧振器的最大動態電阻.

重新排列并選擇XC3=XC4,

在10MHz,C3和C4的(假定相等)是值:

C3=C4=1/2πf X C4=123.3pF

選擇行業標準電容值為120pF,石英晶體諧振器兩端的負載電容為C3和C4的串聯:1/(1/C3+1/C4)=60pF.但是,為確保在所需頻率下振蕩,必須通過指定的負載電容(20pF)加載晶體諧振器.這可以通過將C3和C4的值各自降低到40pF來實現,但結果是非常大的過量增益(RIN + R1MAX),這可能對振蕩器的噪聲性能有害.設置20pF凈負載電容的首選方法是引入一個30pF串聯電容(圖1b完成電路中的C5 ).

集電極開路引腳有效-低OUT和OUT(引腳5和8)提供差分輸出或兩個單端輸出.每個引腳可吸收大約2.5mA的靜態電流,每個引腳都需要上拉至VCC.RF扼流圈或電阻可用作上拉電阻,但對于差分輸出,請務必在每條線上使用相同的類型.請注意,大于100Ω的電阻上拉會導致電壓過低.對于50Ω負載,單端輸出電平約為-6dBm(320mVP-P),具有RF扼流圈上拉,約-13dBm(140mVP-P),具有50Ω電阻上拉.

正在載入評論數據...

相關資訊

- [2025-01-06]輕松管理EMI-泰藝電子低EMI晶振(SX與...

- [2025-01-06]用于 PCIe 6.0/5.0 汽車應用的低功耗...

- [2024-12-18]Q-Tech宣布推出AXTAL GHz系列全系列

- [2024-12-07]Silicon Labs 在 ESG 方面取得卓越成...

- [2024-12-05]高頻和低抖動的 SPXO SG2016CBN,SG25...

- [2024-12-04]Statek推出 ULPXO 超低功耗晶體振蕩器...

- [2024-12-04]JT21GL(E)和JT11GL(E)是Jauch頻率產品...

- [2024-11-28]Endura 低相位噪聲 Super-TCXO

銷售代表

銷售代表